# Designing asynchronous circuits with timing conditions

Vision statement for possible CAD development under Workcraft

### Original document:

A. Yakovlev, Synthesis from timing diagrams: rough notes and examples, Tech Memo, March 7, 1998; written on the basis of discussions with Ed Cerny and Luciano Lavagno

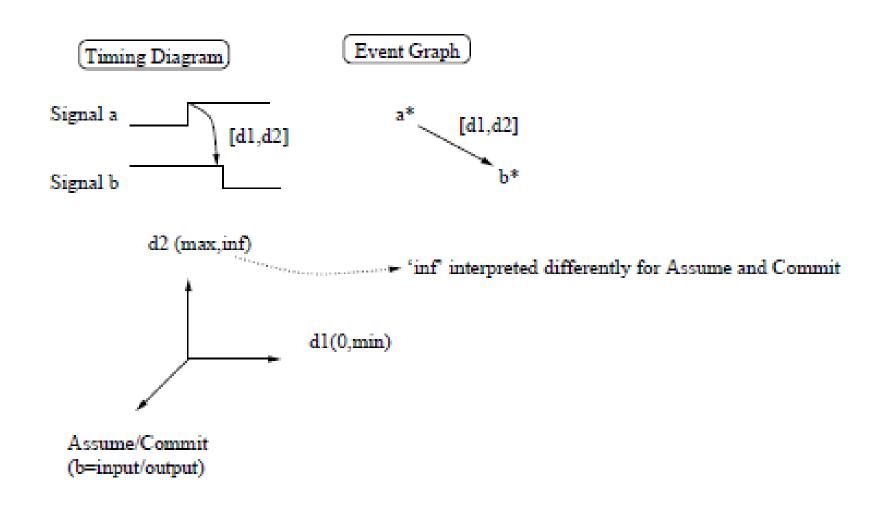

### Basic classification of timing conditions

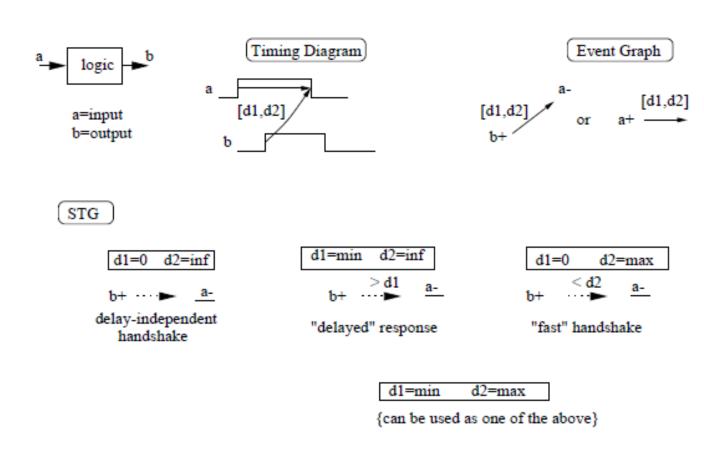

### STG interpretation of Assume conditions

- (1) Case  $d1 = 0, d2 = \infty$ Corresponds to delayindependent handshake

- (2) Case  $d1=min>0, d2=\infty$ Corresponds to delayed (by min value) response from the environment

- (3) Case  $d1=0, d2=max<\infty$ Corresponds to bounded response, e.g. from clock signal

- (4) Case  $d1 = min > 0, d2 = max < \infty$

Combination of (2) and (3), i.e. imaginary handshake with input clock

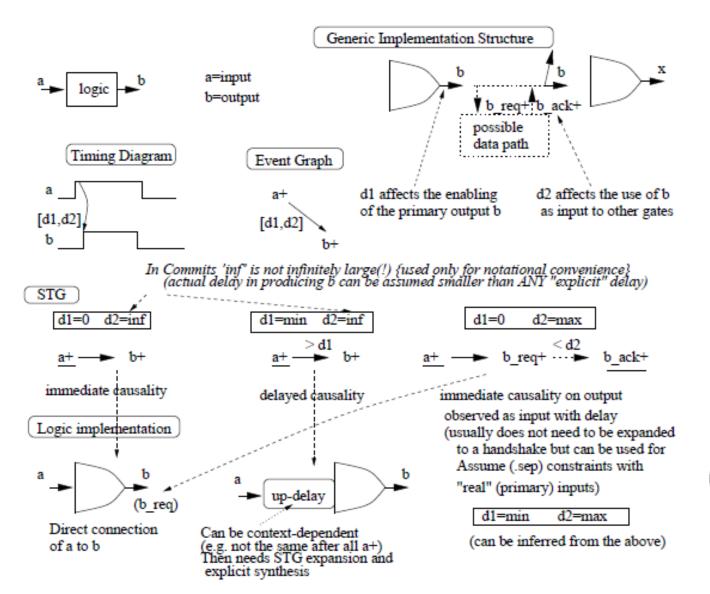

### STG interpretation of commits

- (1) Case  $d1 = 0, d2 = \infty$ Corresponds to immediate causality between input a and the logic producing output b

- (2) Case d1 = min > 0,  $d2 = \infty$ Corresponds to delayed causality, e.g. for producing skew compensation (bundled data strobe or setup)

- (3) Case d1 = 0,  $d2 = max < \infty$ Corresponds to immediate causality but observing of the output b may be after some (up to max) delay

- (4) Case  $d1=min>0, d2=max<\infty$ Combination of (2) and (3)

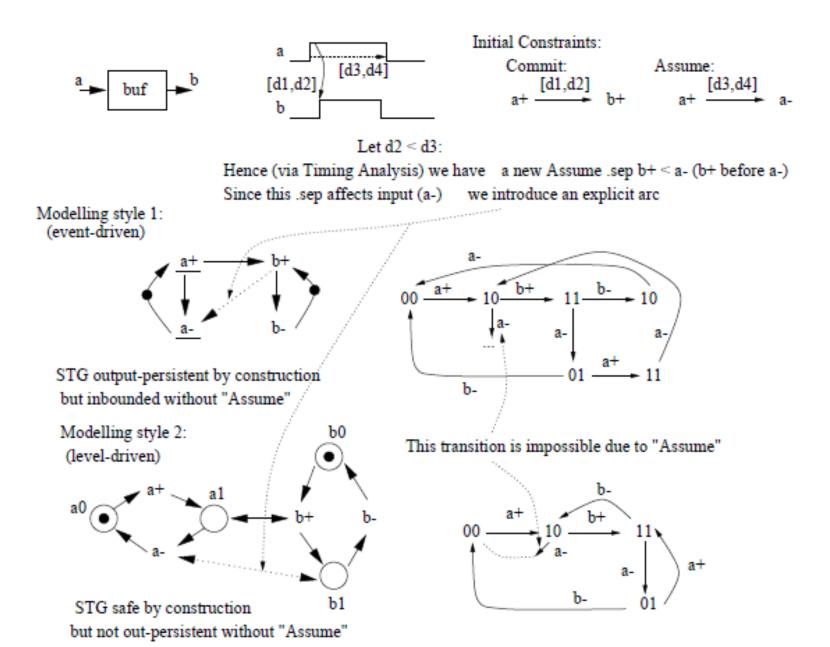

# Simple buffer example

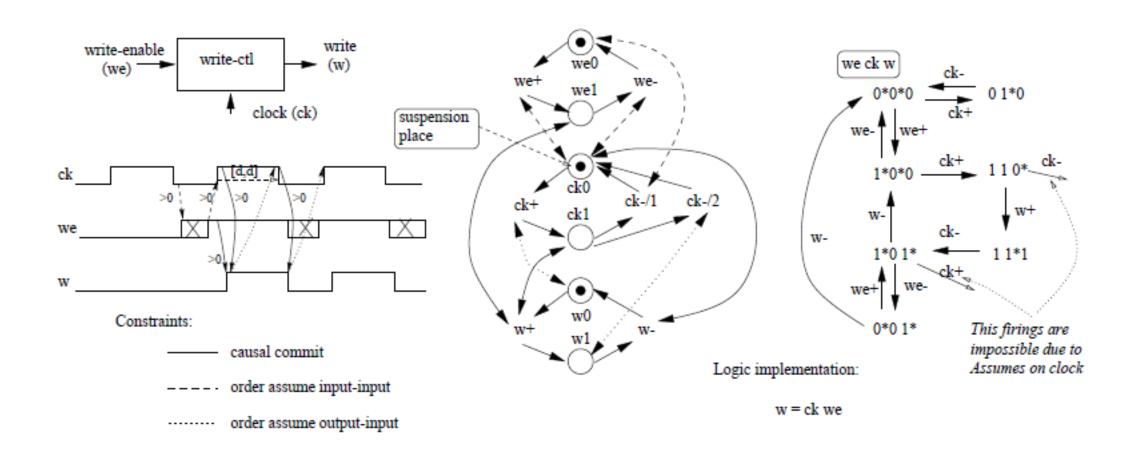

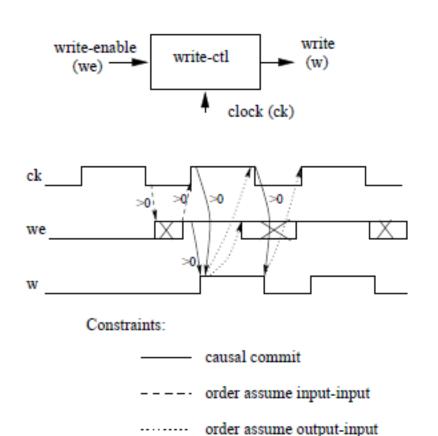

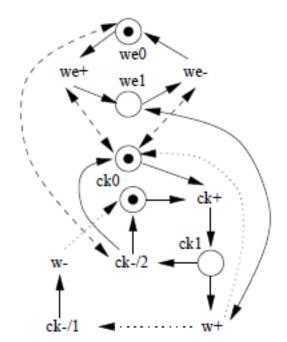

### Clocked write controller

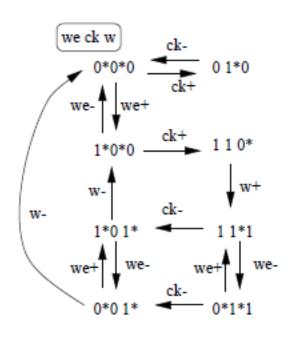

### Very simple clocked write controller

Here we allow 'we' to resume its change after 'w' goes high

Logic implementation:

w = ck we + ck w

w = ck we if, additionally, .sep ck-/1 < we- is applied

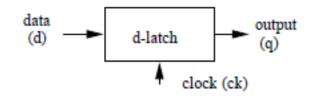

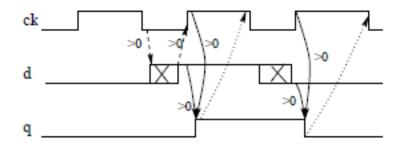

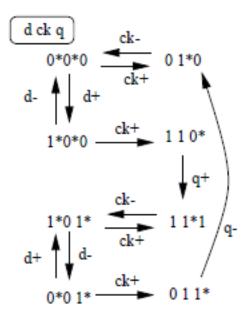

### Clocked D-latch

#### Constraints:

——— causal commit

--- order assume input-input

····· order assume output-input

Logic implementation:

$$q = ck d + ck' q$$

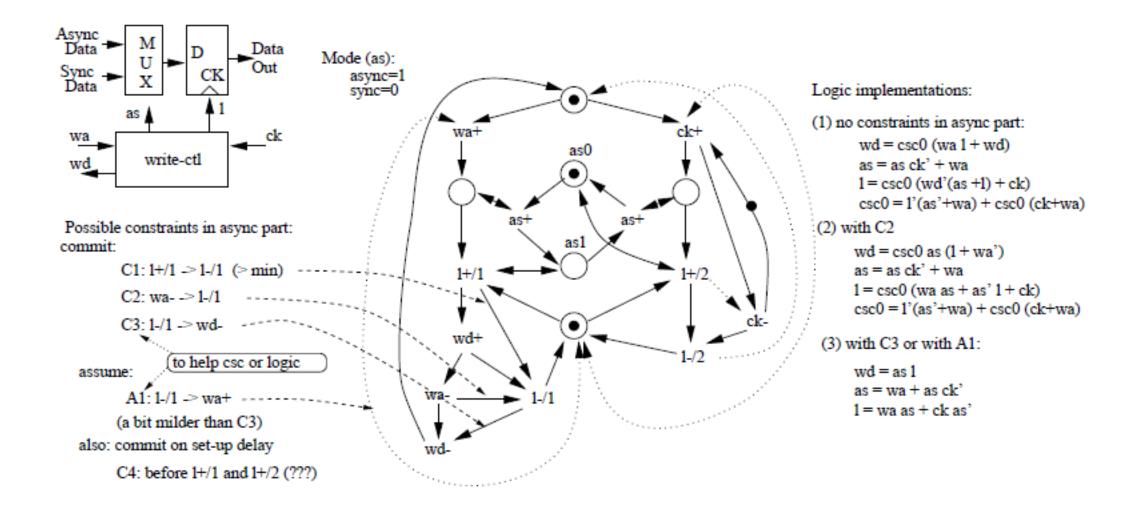

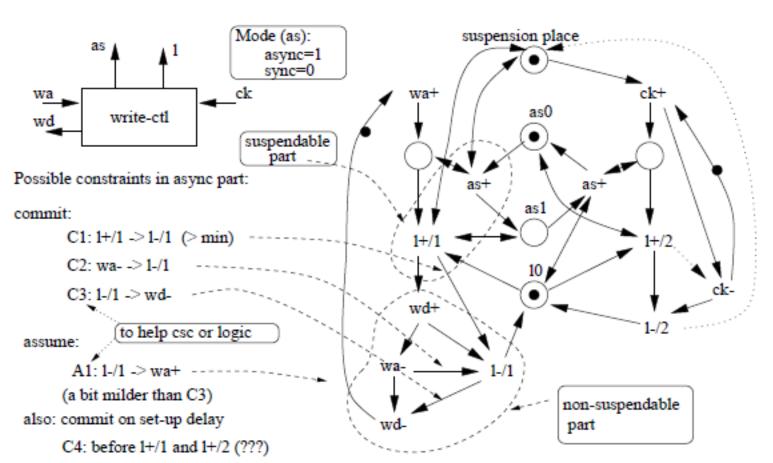

## Dual (Sync/Async) mode write ctl with external choice

## Dual (Sync/Async) mode write ctl with preemption by Sync

#### Logic implementations:

(1) no constraints in async part:

```

wd = csc0 (as 1 + wd)

as = wa ck' wd' 1' + as (ck' + 1)

1 = csc0 wd' as (ck' +1) + ck as'

csc0 = wa (1 + csc0 + as')

```

(3) with C3:

```

wd = as 1

as = wa ck' 1' + as (1 + ck')

1 = wa ck' as + ck (wa 1 + as')

```

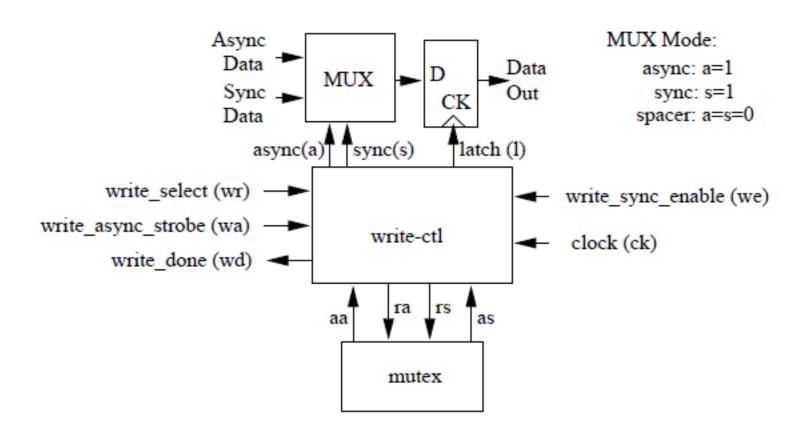

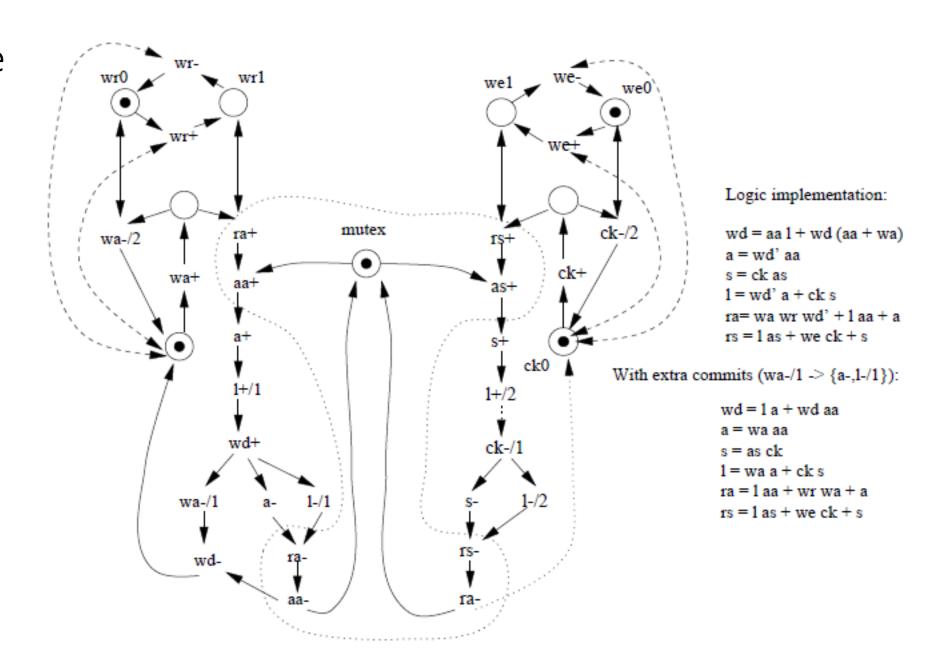

### Dual (Sync/Async) mode write ctl with Mutex

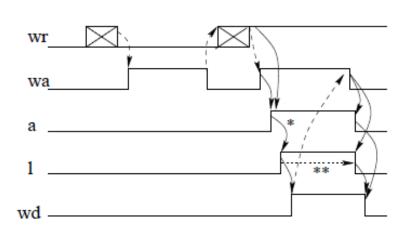

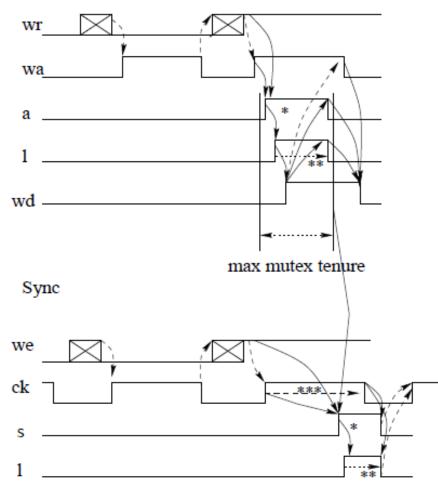

### Dual mode write ctl: timing diagrams)

Async 2

Async1

special commit constraints:

- \* maybe min set-up time

- \*\* maybe min hold time

special assume constraint:

\*\*\* length of clock pulse must allow for at least one mutext tenure on async (to avoid missing sync cycles)

Dual mode write ctl with Mutex: STG and logic

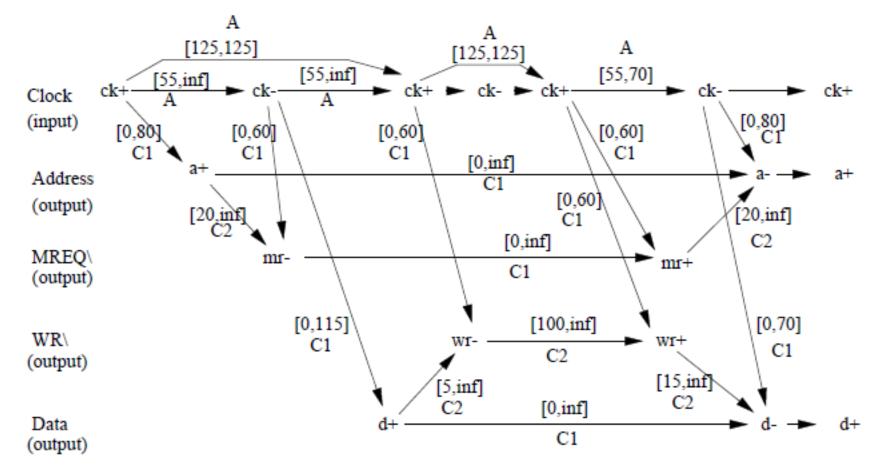

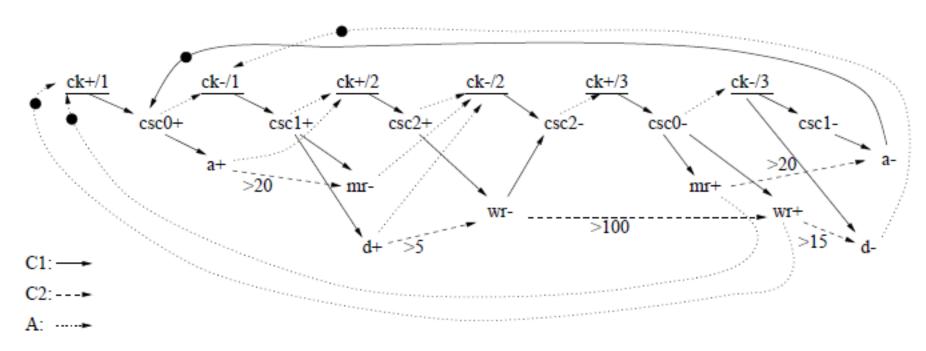

Example of Z84 write i/f: Initial Event Graph

Constraint types: commit ( $\{I,O\} \rightarrow O$ ) and assume ( $\{I,O\} \rightarrow I$ )

commit 1 (C1): [0,max] or [0,inf] => 'immediate causal' ASAP (for enabling); but maybe as long as max if with max, this can be used as assume (?)

commit 2 (C2): [min, inf] => 'delayed causal' ASAP (via min delay); must not be less than min

assume (A): [min,max] => 'timing assumptions' to avoid inconsistence, nonpersistence, state coding conflicts and to optimize logic (wrt area and/or speed)

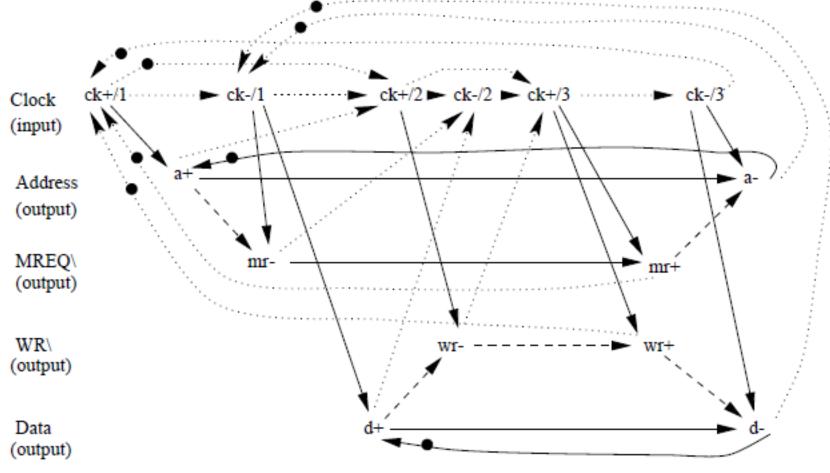

Example with Z84 write i/f: deriving STG from initial constraints

Constraint types: commit ( $\{I,O\} \rightarrow O$ ) and assume ( $\{I,O\} \rightarrow I$ )

commit 1 (C1): [0,max] or [0,inf] => 'immediate causal' ASAP (for enabling); but maybe as long as max if with max, this can be used as assume (?)

commit 2 (C2): [min, inf] => 'delayed causal' ASAP (via min delay); must not be less than min

assume (A): [min,max] => 'timing assumptions' to avoid inconsistence, nonpersistence, state coding conflicts

and to optimize logic (wrt area and/or speed)

Additional assume constraints inferred from C1 (with max) and A to help state coding and logic

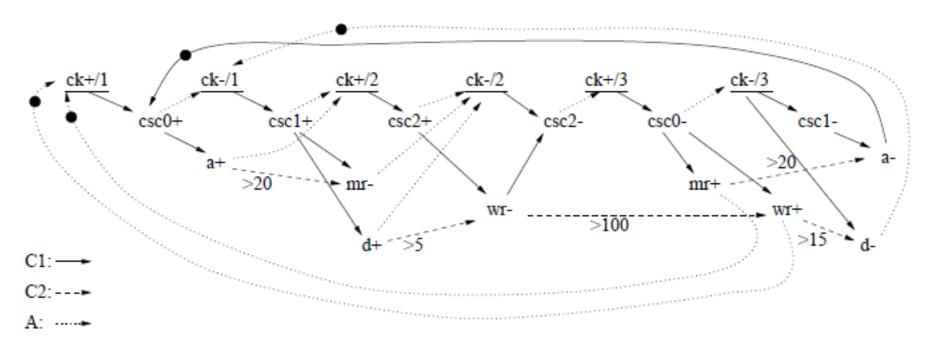

### Example with Z84 write i/f: STG-based synthesis

### Logic implementation:

```

a = \csc 0 + \csc 1 + \underline{mr}'

csc 0 = \csc 2 + ck \ a' + \csc 0 \ (ck' + wr)

csc 1 = \csc 0 \ ck' + \csc 1 \ ck

csc 2 = ck \ wr \ csc 0 \ csc 1 + \csc 2 \ (ck + wr)

d = \csc 1(\csc 0 + ck) \ \underline{wr}'

```

commit C2 constraints have to be satisfied by inserting delays into trigger inputs

## Example with Z84 write i/f: using stricter (burst) constraints

Logic implementation:

```

a = \csc 0 + \csc 1 + \underline{mr}

csc 0 = \csc 2 + ck \ a' + \csc 0 \ (ck' + wr)

csc 1 = \csc 0 \ ck' + \csc 1 \ ck

csc 2 = ck \ wr \ csc 0 \ csc 1 + \csc 2 \ (ck + wr)

d = \csc 1(\csc 0 + ck) \ \underline{wr}

```

commit C2 constraints have to be satisfied by inserting delays into trigger inputs

## STG synthesis problems

**Problem 5.1** Given a Timing Diagram specification (or better say, an Event Graph, whose arcs are annotated with timing constraints), synthesize an 'equivalent' STG with three types of arcs (or places and arcs if choice is involved): "immediate causality" arcs, "delayed causality" arcs and "input order" arcs.

**Problem 5.2** Find an optimal (speed/area of future logic) asynchronous schedule in terms of "precedence" (b always occurs after a) and "delayed precedence" (b always occurs after a with a delay of  $\delta$  units <sup>4</sup>) arcs that satisfies the original Timing Diagram (Event Graph).

### Related work

A. El-Aboudi, E. -. Aboulhamid and E. Cerny, "Synthesis of interface controllers from timing diagram specifications," *Proceedings of the IEEE 1998 Custom Integrated Circuits Conference (Cat. No.98CH36143)*, Santa Clara, CA, USA, 1998, pp. 89-92.

doi: 10.1109/CICC.1998.694913

P. Vanbekbergen, G. Goossens and H. De Man, "Specification and analysis of timing constraints in signal transition graphs," [1992] Proceedings The European Conference on Design Automation, Brussels, Belgium, 1992, pp. 302-306.

doi: 10.1109/EDAC.1992.205943

K. -. Chung, R. K. Gupta and C. L. Liu, "An algorithm for synthesis of system-level interface circuits," *Proceedings of International Conference on Computer Aided Design*, San Jose, CA, USA, 1996, pp. 442-447.

doi: 10.1109/ICCAD.1996.569835